IC (Integrated Circuit): 집적회로

> 능동소자: 작은 신호 (전력, 전압, 전류 등)를 넣어 큰 출력 신호로 변화시킬 수 있는 전자 부품 소자

ex) OPAMP, Diode, Transistor

> 수동소자: 공급된 전력을 소비, 축적, 방출하는 소자

ex) R, L, C

IC의 개념

> Silicon paper 위에서 여러 기능을 수행하는 회로들이 IC에 구현되면서 IC 자체가 하나의 시스템처럼 동작할 수 있음

> 하나의 시스템이 반도체 IC에 구현되는 것: SOC (System On Chip)

> 반도체 chip을 PCB에 장착하기 위해서는 Epoxy와 같은 플라스틱 물질로 둘러싸는 포장 과정 (Packaging: IC칩을 외부로부터 보호하고, 단자간 연결을 위한 작업)이 필요

IC의 분류

>Analog IC: Analog signal을 처리하는 IC

-> 신호가 선형 특성, 시간에 따른 연속성을 가짐

ex) OPAMP IC (신호 증폭), PMIC (Power Management IC: 회로에서 필요한 여러 직류 전압들을 만들어주는 전력 관리용 IC)

> Digital IC: Logic '0', '1'을 나타내는 두 가지 신호 전압 레벨

-> 논리 게이트 IC: BJT=> TTL/ MOSFET => CMOS (다양한 형태의 디지털 회로를 구현할 수 있음)

(TTL과 CMOS의 차이점: CMOS는 정적 상태 동안 전력을 소비하지 않지만 클록 속도에 따라 전력 소비가 증가한다는 특징이 있습니다. 반면, TTL은 일정한 전력 소비 수준을 가지고 있습니다. CMOS는 전류 요구 사항이 낮기 때문에 전력 소비가 제한되고, 회로가 더 저렴하며, 전력 관리를 위해 설계하기 쉽습니다)

> Memory IC: 많은 양의 Digital data를 저장 (저장 용량과 동작 속도가 중요한 기능)

->ROM (Read Only Memory: 저장된 정보를 읽기만 가능): 제한적이지만 쓰기기능이 추가된 형태가 많이 사용됨

-> RAM (Random Access Memory): 속도와 저장용량이 높음

-> Flash Memory: 읽고 쓰기가 가능하며 전원이 공급되지 않아도 저장한 정보를 기억 (ex. SSD)

=> 집적도의 향상은 반도체 미세공정 발달 덕분이며, 3차원 방식의 반도체 공정 및 나노 전자소자 등 새로운 기술들이 발전하면서 IC의 집적도가 더욱 높아질 것이라 예상됨

> MSI (Medium Scale Integration): 레지스터, 카운터처럼 간단한 기능 수행

> LSI (Large Scale Intetragration): 1Kbit RAM 및 8 ~ 16 bit CPU

> VLSI (Very Large Scale Integration): 1Mbits RAM 및 32 bit CPU

> ULSI (Ultra Large Scale Integration)" 펜티엄 이상의 CPU

IC의 장점

1. 납땜없이 인쇄기술과 Etching 공정을 이용한 회로 구현 가능: 고장이 적어 신뢰성이 향상될 수 있음

2. 대량 생산이 가능하여 가격적 측면에서 유리함

3. 많은 부품들이 집적되어 회로의 소형화와 경량화에 유리함

4. 부품간의 거리가 짧아, 선로에 존재하는 인덕턴스, 카패시턴스 값이 작으며 이에 고속 동작이 유리함

5. 소비전력이 작아 저전력 회로에 유리하다

IC의 단점

1. 열에 약함: IC에 들어가는 Pacakage는 열을 외부로 잘 방출해야 하며, 온도를 낮추기 위해 방열판 혹은 쿨러 등을 이용해야함

2. 큰 값의 L, C값을 IC 내부에 구현하기 어려움: 어느 정도 큰 R, L, C 값이 필요한 경우 IC 외부에서 연결해야 함

팬아웃 (Fan-out)

> 논리 회로에서 하나의 논리 게이트의 출력이 얼마나 많은 논리 게이트의 입력으로 사용되는지의 정도

(팬 아웃이 크다 = 하나의 출력이 많은 논리게이트의 입력으로 사용된다)

> IC의 출력단

- 신호가 전압의 형태로 나옴

- 출력단에 연결되는 부하가 필요로 하는 전류도 공급

-> 전압이 왜곡없이 출력되면서 전류도 잘 내어줄 수 있는 형태의 회로구성을 해야함

> 디지털 논리게이트

- CMOS 논리게이트: 입력단이 MOSFET의 게이트 단자부분이여서 거의 전류가 흐르지 않는 구조

(Thus, 이론적으로 CMOS의 팬아웃이 커야하지만 Parastic capacitance가 게이트 입력단에 존재하기 떄문에, 입력단을 많이 사용하게 되면 (병렬) Capacitance값이 커져 펄스형태 신호의 충방전이 지연되어 버리기 때문에, 결국 COMS도 제한적인 Fan-out을 가지게 됨)

- TTL 게이트: Logic '0', '1'이 나타내는 각각의 전압이 입력될 때ㅡ 어느 정도의 전류가 TTL 게이트의 입력단으로 흘러들어가야 하는 구조

-> 뒷 단의 입력단자로 흘러가야 하는 전류를 앞단 IC의 출력단자에서 공급해야 함!

=> 논리게이트 출력 단자의 전류 공급 능력에 따라 그 출력 단자에 연결될 수 있는 논리 게이트의 수가 제한을 받게 되며, 이때 하나의 논리게이트 출력 단자에 연결 가능한 논리 게이트 입력의 최대 갯수를 팬 아웃 (Fan-out)이라고 함

IC 출력단

> 오픈 컬렉터 (Open collector) 구조 (오픈 드레인 구조와 유사)

- BJT의 컬렉터 단자가 IC의 외부로 연결

- 동작 전압이 서로 다른 IC까지 데이터를 주고 받는 것을 쉽게 구현 가능: I^2C 통신과 같이 하나의 전송선을 공유하는 통신 방식을 회로로 구현하기 위해 많이 사용

- 외부 출력단자에는 외부 출력전압을 자유롭게 성정하여 플로팅 상태를 막을 수 있음 (Full-up 저항 형태)

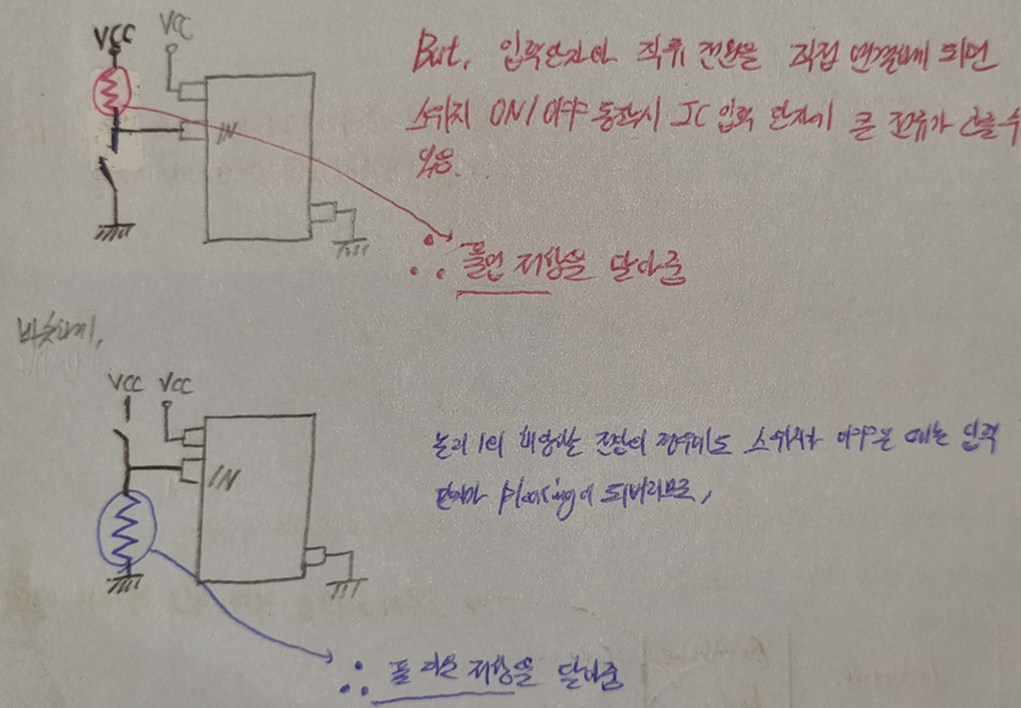

> Full-up/ Full-down 저항: 전압의 범위가 정의되지 않은 입, 출력의 범위에 들어가게 되면 오동작을 일으키게 되므로 사용 (플로팅을 막기 위해)

- Floating (플로팅)이 되면 잡음의 영향 등을 쉽게 받을 수 있어, 입력 단자의 전압이 정의되지 않은 구간의 값이 될 수 있음

- 해결책: 풀업, 풀다운 저항

> 오픈 컬렉터 출력의 응용:

- 서로 다른 동작 전압을 가지는 두 IC를 연결할 때 동작 전압이 다르면 Logic을 나타내는 전압의 레벨도 다르므로 주의해야함: Level Shifter라는 별도의 회로를 사용해 전압을 변환해주어야 함 (기존 해결책)

하지만, 오픈 컬렉터 출력 구조를 활용한다면, IC간의 연결을 쉽고 간단하게 구성할 수 있음